INTC

Allwinner SoCs have a bespoke interrupt controller. It was originally the only interrupt controller on the chip. On SoCs with a GIC (sun6i and newer), it sits between the NMI pin and a GIC input. It is responsible for controlling the NMI trigger type (high/low/rising/falling). On SoCs with an AR100, it serves as the interrupt controller for that CPU.

INTC

sun4i/sun5i SoCs (A10, A13) did not have a GIC, and used this hardware exclusively. See the A13 manual for a detailed register description.

Driver

This interrupt controller uses the drivers/irqchip/irq-sun4i.c driver in Linux.

NMI Controller

After Allwinner switched to using a GIC, but before they added a power management coprocessor, there was no need for a full INTC. SoCs like the A20 have a stripped-down version of the hardware, that only manages the trigger type for the NMI.

Driver

This interrupt controller uses the drivers/irqchip/irq-sunxi-nmi.c driver in Linux.

R_INTC

The R_INTC is the secondary interrupt controller in sun8i/sun50i SoCs that contain the AR100 coprocessor. It is closely related to the original sun4i INTC. While stripped down some, it is much closer to the original feature set than it is to the A20 NMI controller.

Hardware Architecture

See the A13 manual for register descriptions. Only the first register of each type is implemented, so a maximum of 32 IRQs are supported (but see below). The priority logic appears not to be implemented, as setting any bit in the RESP register stops the AR100 from receiving interrupt exceptions from all IRQs.

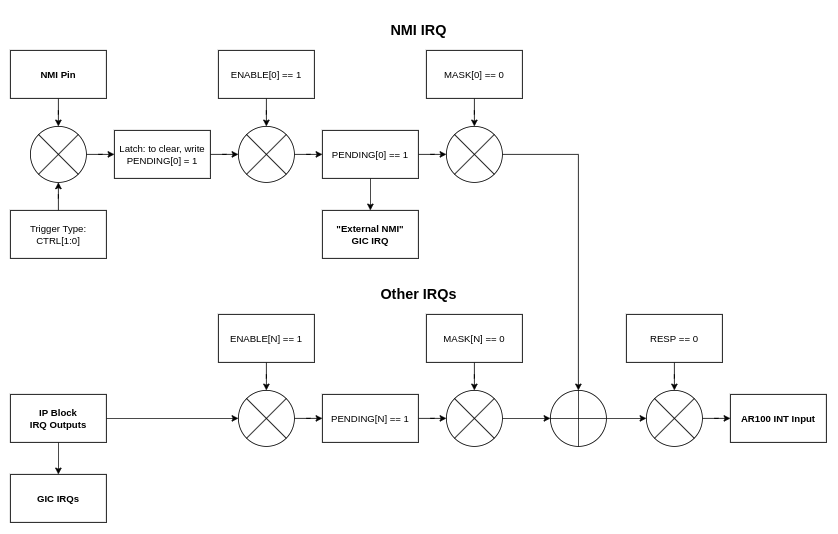

The image below shows how the various registers control the IRQ flow. Note that the NMI IRQ has a latch (separate from any rising/falling trigger) that must be ACKed before the signal to the GIC will be deasserted.

IRQ Mapping

The first IRQ is always the NMI. The order of the next 15 IRQs matches the order the corresponding inputs to the GIC. Then there is a region of uncertainty, containing at least the MSGBOX IRQ. The remainder of the IRQs are multiplexed from the same sources as the first hundred or so SPI IRQs.

The multiplexing of the individual IRQs in each "SPI IRQ" group is controlled by bits in registers 0xc0-0xcc, with one bit for each IRQ. There is no way (from R_INTC) to get the status of one of these multiplexed IRQs. If the CPU cluster is powered on, you can read the GICD ISPENDRs. Otherwise, you will have to check each IRQ source individually.

H3

Same as A64 and H5. Verified with HSTIMER (SPI 51) => bit 25.

A64/H5

| Bit | IRQ | Notes |

|---|---|---|

| 0 | NMI | |

| 1 | R_TIMER0 | |

| 2 | R_TIMER1 | |

| 3 | N/A | |

| 4 | R_WDOG | |

| 5 | R_CIR_RX | |

| 6 | R_UART | |

| 7 | R_RSB | Not present on H-series SoCs |

| 8 | R_ALARM0 | |

| 9 | R_ALARM1 | |

| 10 | R_TIMER2 | |

| 11 | R_TIMER3 | |

| 12 | R_I2C | |

| 13 | R_PIO_PL | |

| 14 | R_TWD | |

| 15 | N/A | |

| 16 | ??? | Probably SPINLOCK |

| 17 | MSGBOX | |

| 18 | ??? | Probably DMA |

| 19 | SPI 0-7 | Verified with I2C0 (6) |

| 20 | SPI 8-15 | |

| 21 | SPI 16-23 | |

| 22 | SPI 24-31 | Verified with THS (31) |

| 23 | N/A | SPI 32-39 are the same as bits 0-7 |

| 24 | N/A | SPI 40-47 are the same as bits 8-15 |

| 25 | SPI 51-55 | The bits in 0xc4 for SPI 48-50 are forced low |

| 26 | SPI 56-63 | |

| 27 | SPI 64-71 | |

| 28 | SPI 72-79 | Verified with OHCI0 (75) |

| 29 | SPI 80-87 | |

| 30 | SPI 88-95 | |

| 31 | SPI 96-99 | The bits in 0xcc for SPI 100-103 are forced low |

H6

| Bit | IRQ | Notes |

|---|---|---|

| 0x40.0 | NMI | |

| 0x40.1 | R_TIMER0 | |

| 0x40.2 | R_TIMER1 | |

| 0x40.3 | R_TIMER2 | |

| 0x40.4 | R_TIMER3 | |

| 0x40.5 | R_ALARM0 | |

| 0x40.6 | R_ALARM1 | |

| 0x40.7 | R_WDOG | |

| 0x40.8 | R_TWD | |

| 0x40.9 | R_PIO_PL | |

| 0x40.10 | R_UART | |

| 0x40.11 | R_I2C | |

| 0x40.12 | R_RSB | |

| 0x40.13 | R_CIR_RX | |

| 0x40.14 | R_W1 | |

| 0x40.15 | R_PIO_PM | |

| 0x40.16 | CPUIDLE | From arisc BSP source |

| 0x40.17 | GIC_OUT | From arisc BSP source |

| 0x40.18 | SPINLOCK | From arisc BSP source |

| 0x40.19 | MSGBOX | From arisc BSP source |

| 0x40.20 | DMA | From arisc BSP source |

| 0x40.21 | SPI 0-7 | Verified with I2C3 (7) |

| 0x40.22 | SPI 8-15 | Verified with THS (15) |

| 0x40.23 | SPI 16-23 | Verified with I2S2 (20) |

| 0x40.24 | SPI 24-31 | Verified with OHCI3 (29) |

| 0x40.25 | SPI 32-39 | |

| 0x40.26 | SPI 40-47 | Verified with HSTIMER (46) |

| 0x40.27 | SPI 48-55 | Verified with TIMER0 (48), TIMER1 (49), GPIOF (53) |

| 0x40.28 | SPI 56-63 | Verified with GPIOH (59) |

| 0x40.29 | SPI 64-71 | |

| 0x40.30 | SPI 72-79 | |

| 0x40.31 | SPI 80-87 | Verified with IRQMMU (85) |

| 0x44.0 | SPI 88-95 | |

| 0x44.1 | SPI 96-103 | |

| 0x44.2 | SPI 104-111 | |

| 0x44.3 | SPI 112-119 | |

| 0x44.4 | SPI 120-127 |

Driver

This interrupt controller currently uses the drivers/irqchip/irq-sunxi-nmi.c driver in Linux as well, but a new driver is needed to support preconfiguring the wakeup IRQs for the AR100.