A10-MID UART

This page describes how to find serial on a totally underdocumented device that no-one but the author of this page knows how to identify. This makes this page totally useless, but since it has some actual content, it pays to not remove it, yet.

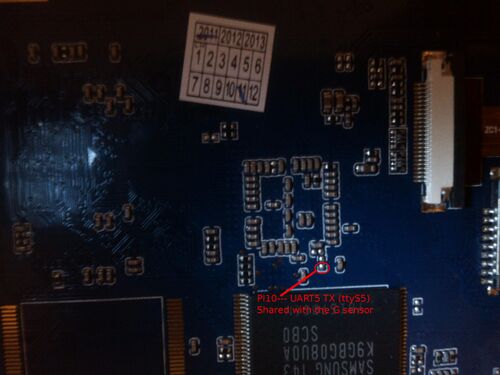

After 3 days of probing my tablet with an oscilloscope I can report that I (specing@#arm-netbook) have (28.6.2012) found an alternative serial port (No more mmc trade-offs :) ). The RX pin should be one of those pins near it.

The serial port is located on the back of the board, near to the NAND and behind the A10.

The serial port in question is UART5 (ttyS5) on PI10:

[uart_para5] uart_used = 1 uart_port = 5 uart_type = 2 uart_tx = port:PI10<3><default><default><default> uart_rx = port:PI11<3><default><default><default>

The tx pin is also shared with the G sensor.

More board pictures and nanda dumps are available from:

my website (DEAD)

Finding UART

You can use the serial_spammer.c program available from my site to output a specific byte over and over again on the serial ports (I have uploaded a precompiled statically-linked binary for those who do not have Gentoo at hand :) ).

Use the following map I scraped from the a10 datasheet to help you test:

pin cfg pin cfg

UART0 PB22-2 F PF02-4 Ff(mmc)

PB23-2 PF04-4

UART1 PA10-4

PA11-4

UART2 PI18-3 F PA02-4 F

PI19-3 PA03-4

UART3 PG06-4 F PH00-4 Ti

PG07-4 PH01-4 (mmc conflict)

UART4 PG10-4 F PH04-3 USB

PG11-4 PH05-3

UART5 PI10-3 Ff PH06-4 USB F

PI11-3 PH07-4

UART6 PA12-3 F PI12-3 T

PA13-3 PI13-3

UART7 PA14-3 F PI20-3 F

PA15-3 PI21-3

You can ignore F(fully probed) and f(found) notes, they were used by me to keep track

Note: I have tried to enable all eight serial ports at once through script.bin, but it seems that that number is limited to 4 at a time. Maybe whoever configured the stock kernel did not enable

[*] "Device drivers" -> "Character devices" -> "Serial drivers" -> "Support more than 4 legacy serial ports"

or some other option on the same page. The meaning of the error is still unknown to me:

# dmesg | grep uart <3>[ 0.290000] sw-uart.1: failed to claim resource 0 <3>[ 0.290000] sw-uart.6: failed to claim resource 0 <6>[ 0.290000] sw-uart.0: ttyS0 at MMIO 0x1c28000 (irq = 1) is a sw-uart0 <6>[ 0.300000] sw-uart.5: ttyS5 at MMIO 0x1c29400 (irq = 18) is a sw-uart5

u-boot fixes

Im currently using the default branch of git://github.com/hno/uboot-allwinner.git

Note: u-boot have since moved to https://github.com/linux-sunxi/u-boot-sunxi.git

To enable the sixth UART (ttyS5), you have to (thanks hno) change the following:

diff --git a/arch/arm/cpu/armv7/sunxi/board.c b/arch/arm/cpu/armv7/sunxi/board.c

index f6f9486..61b6da3 100644

--- a/arch/arm/cpu/armv7/sunxi/board.c

+++ b/arch/arm/cpu/armv7/sunxi/board.c

@@ -74,8 +74,8 @@ sunxi_boot_type_t boot_from(void) {

int gpio_init(void) {

/* config uart pin */

- sunxi_gpio_set_cfgpin(SUNXI_GPB(22), SUNXI_GPB22_UART0_TX);

- sunxi_gpio_set_cfgpin(SUNXI_GPB(23), SUNXI_GPB23_UART0_RX);

+ sunxi_gpio_set_cfgpin(SUNXI_GPI(10), 3);

+ sunxi_gpio_set_cfgpin(SUNXI_GPI(11), 3);

return 0;

}

diff --git a/arch/arm/cpu/armv7/sunxi/clock.c b/arch/arm/cpu/armv7/sunxi/clock.c

index 772673a..639e264 100644

--- a/arch/arm/cpu/armv7/sunxi/clock.c

+++ b/arch/arm/cpu/armv7/sunxi/clock.c

@@ -73,7 +73,7 @@ int clock_init(void) {

sr32(&ccm->apb1_clk_div_cfg, 16, 2, APB1_FACTOR_N);

sr32(&ccm->apb1_clk_div_cfg, 0, 5, APB1_FACTOR_M);

/* open the clock for uart0 */

- sr32(&ccm->apb1_gate, 16, 1, CLK_GATE_OPEN);

+ sr32(&ccm->apb1_gate, 21, 1, CLK_GATE_OPEN);

#ifdef CONFIG_SPL_BUILD

diff --git a/include/configs/sun4i.h b/include/configs/sun4i.h

index 3cb9e03..6a953e4 100644

--- a/include/configs/sun4i.h

+++ b/include/configs/sun4i.h

@@ -53,10 +53,14 @@

#define CONFIG_SYS_NS16550_SERIAL

#define CONFIG_SYS_NS16550_REG_SIZE (-4) /* ns16550 reg in the low bits of cpu reg */

#define CONFIG_SYS_NS16550_CLK (24000000)

-#define CONFIG_SYS_NS16550_COM1 SUNXI_UART0_BASE

+#define CONFIG_SYS_NS16550_COM1 SUNXI_UART5_BASE

#define CONFIG_SYS_NS16550_COM2 SUNXI_UART1_BASE

#define CONFIG_SYS_NS16550_COM3 SUNXI_UART2_BASE

#define CONFIG_SYS_NS16550_COM4 SUNXI_UART3_BASE

+#define CONFIG_SYS_NS16550_COM5 SUNXI_UART4_BASE

+#define CONFIG_SYS_NS16550_COM6 SUNXI_UART0_BASE

+#define CONFIG_SYS_NS16550_COM7 SUNXI_UART6_BASE

+#define CONFIG_SYS_NS16550_COM8 SUNXI_UART7_BASE

#define CONFIG_CONS_INDEX 1 /* which serial channel for console */

@@ -158,10 +162,10 @@

#define CONFIG_BOOTCOMMAND "run boot.scr setargs boot_mmc"

#define CONFIG_EXTRA_ENV_SETTINGS \

- "console=ttyS0,115200\0" \

+ "console=ttyS5,115200\0" \

"root=/dev/mmcblk0p2\0" \

"panicarg=panic=10\0" \

- "extraargs=\0" \

+ "extraargs=rootwait\0" \

"loglevel=8\0" \

"setargs=setenv bootargs console=${console} root=${root}" \

" loglevel=${loglevel} ${panicarg} ${extraargs}\0" \

The same patch is also available here (DEAD).

Kernel

Im using the kernel from git://github.com/amery/linux-allwinner I have had some problems with it remapping serial port numbers if not all serial ports before the uart5 are enabled (0,1,2,3,4) in script.bin. Currently it gets me to the login prompt and I have yet to find the rx pin.