# **AXP805** Datasheet

### PMIC for Multi-Core High-Performance System

Version 1.0

Nov.14, 2017

Copyright © 2017 X-Powers Limited. All Right Reserved.

### Declaration

THIS DOCUMENTATION IS THE ORIGINAL WORK AND COPYRIGHTED PROPERTY OF X-POWERS. REPRODUCTION IN WHOLE OR IN PART MUST OBTAIN THE WRITTEN APPROVAL OF X-POWERS AND GIVE CLEAR ACKNOWLEDGEMENT TO THE COPYRIGHT OWNER.

THE PURCHASED PRODUCTS, SERVICES AND FEATURES ARE STIPULATED BY THE CONTRACT MADE BETWEEN X-POWERS AND THE CUSTOMER. PLEASE READ THE TERMS AND CONDITIONS OF THE CONTRACT AND RELEVANT INSTRUCTIONS CAREFULLY BEFORE USING, AND FOLLOW THE INSTRUCTIONS IN THIS DOCUMENTATION STRICTLY. X-POWERS ASSUMES NO RESPONSIBILITY FOR THE CONSEQUENCES OF IMPROPER USE(INCLUDING BUT NOT LIMITED TO OVERVOLTAGE, OVERCLOCK, OR EXCESSIVE TEMPERATURE).

THE INFORMATION FURNISHED BY X-POWERS IS PROVIDED JUST AS A REFERENCE OR TYPICAL APPLICATIONS. ALL STATEMENTS, INFORMATION, AND RECOMMENDATIONS IN THIS DOCUMENT DO NOT CONSTITUTE A WARRANTY OF ANY KIND, EXPRESS OR IMPLIED. X-POWERS RESERVES THE RIGHT TO MAKE CHANGES IN CIRCUIT DESIGN AND/OR SPECIFICATIONS AT ANY TIME WITHOUT NOTICE.

NOR FOR ANY INFRINGEMENTS OF PATENTS OR OTHER RIGHTS OF THE THIRD PARTIES WHICH MAY RESULT FROM ITS USE. NO LICENSE IS GRANTED BY IMPLICATION OR OTHERWISE UNDER ANY PATENT OR PATENT RIGHTS OF X-POWERS. THIRD PARTY LICENCES MAY BE REQUIRED TO IMPLEMENT THE SOLUTION/PRODUCT. CUSTOMERS SHALL BE SOLELY RESPONSIBLE TO OBTAIN ALL APPROPRIATELY REQUIRED THIRD PARTY LICENCES. X-POWERS SHALL NOT BE LIABLE FOR ANY LICENCE FEE OR ROYALTY DUE IN RESPECT OF ANY REQUIRED THIRD PARTY LICENCE. X-POWERS SHALL HAVE NO WARRANTY, INDEMNITY OR OTHER OBLIGATIONS WITH RESPECT TO MATTERS COVERED UNDER ANY REQUIRED THIRD PARTY LICENCE.

### **Revision History**

| Revision | Date Description |                         |

|----------|------------------|-------------------------|

| 1.0      | Nov.14, 2017     | Initial release Version |

|          |                  |                         |

|          |                  |                         |

| 2. Feature       .7         3. Typical Application       .8         4. Block Diagram       .9         5. Pin Description       .10         6. Absolute Maximum Ratings       .13         7. Electrical Characteristics       .14         8. Control and Operation       .19         8.1. Master mode       .20         8.2. Slave mode       .20         8.3. Self-work mode       .20         8.4. Sleep and Wakeup       .21         8.4. Sleep and Wakeup       .22         8.5. Reference < Internal Power and Interrupt       .23         8.6. Multi-Power Outputs       .24         8.7. Serial Interface       .25         9. Register       .26         9.1. Register List       .26         9.2. Register Description       .27         9.2.1. REG 00: Startup Source       .27         9.2.2. REG 03: IC Type NO.       .27         9.2.3. REG 04-07: 4 Data Buffers       .27 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Block Diagram       .9         5. Pin Description       .10         6. Absolute Maximum Ratings       .13         7. Electrical Characteristics       .14         8. Control and Operation       .19         8.1. Master mode       .20         8.2. Slave mode       .20         8.3. Self-work mode       .21         8.4. Sleep and Wakeup       .22         8.5. Reference、 Internal Power and Interrupt       .23         8.6. Multi-Power Outputs       .24         8.7. Serial Interface       .25         9. Register       .26         9.1. Register List       .26         9.2. Register Description       .27         9.2.1. REG 00: Startup Source       .27         9.2.2. REG 03: IC Type NO.       .27         9.2.3. REG 04-07: 4 Data Buffers       .27                                                                                                              |

| 5. Pin Description       10         6. Absolute Maximum Ratings       13         7. Electrical Characteristics       14         8. Control and Operation       19         8.1. Master mode       20         8.2. Slave mode       20         8.3. Self-work mode       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                 |

| 6. Absolute Maximum Ratings       13         7. Electrical Characteristics       14         8. Control and Operation       19         8.1. Master mode       20         8.2. Slave mode       20         8.3. Self-work mode       20         8.4. Sleep and Wakeup       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                              |

| 7. Electrical Characteristics       14         8. Control and Operation       19         8.1. Master mode       20         8.2. Slave mode       20         8.3. Self-work mode       20         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                  |

| 8. Control and Operation       19         8.1. Master mode       20         8.2. Slave mode       20         8.3. Self-work mode       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                 |

| 8.1. Master mode       20         8.2. Slave mode       20         8.3. Self-work mode       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                           |

| 8.2. Slave mode.       20         8.3. Self-work mode.       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt.       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface.       25         9. Register       26         9.1. Register List.       26         9.2. Register Description.       27         9.2.1. REG 00: Startup Source.       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers.       27                                                                                                                                                                                                                                                                                                                                                                     |

| 8.3. Self-work mode       21         8.4. Sleep and Wakeup       22         8.5. Reference、 Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.4. Sleep and Wakeup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.5. Reference、Internal Power and Interrupt       23         8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.6. Multi-Power Outputs       24         8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.7. Serial Interface       25         9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9. Register       26         9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.1. Register List       26         9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO.       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.2. Register Description       27         9.2.1. REG 00: Startup Source       27         9.2.2. REG 03: IC Type NO       27         9.2.3. REG 04-07: 4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.2.1. REG 00:       Startup Source       27         9.2.2. REG 03:       IC Type NO.       27         9.2.3. REG 04-07:       4 Data Buffers       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.2.2. REG 03: IC Type NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.2.3. REG 04-07: 4 Data Buffers27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.2.4. REG 10: Output Power on-off Control 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.2.5. REG 11: Output Power on-off Control 228                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.2.6. REG 12: DCDC-A Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.7. REG 13: DCDC-B Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.8. REG 14: DCDC-C Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.9. REG 15: DCDC-D Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.10. REG 16: DCDC-E Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.2.11. REG 17: ALDO1 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.12. REG 18: ALDO2 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.13. REG 19: ALDO3 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.14. REG 1A: DCDC Mode Control 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.2.15. REG 1B: DCDC Mode Control 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.2.16. REG 1C: DCDC Frequency Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.2.17. REG 1D: Output Monitor Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.2.18. REG 1F: IRQ & PWROK& Off Discharge Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.2.19. REG 20: BLDO1 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.20. REG 21: BLDO2 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.21. REG 22: BLDO3 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.22. REG 23: BLDO4 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.23. REG 24: CLDO1 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.24. REG 25: CLDO2 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.25. REG 26: CLDO3 Voltage Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.2.26. REG 31: Power Wakeup Ctrl & VOFF Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.2.27. REG 32: | Power Disable & Power Down Sequence      | 34 |

|-----------------|------------------------------------------|----|

| 9.2.28. REG 35: | Wakeup Pin Function Setting              | 35 |

| 9.2.29. REG 36: | POK Setting                              | 35 |

| 9.2.30. REG 3E: | Interface Mode Select                    | 35 |

| 9.2.31. REG 3F: | Special Control Register                 | 36 |

| 9.2.32. REG 40: | IRQ Enable1                              | 36 |

| 9.2.33. REG 41: | IRQ Enable2                              | 36 |

| 9.2.34. REG 48: | IRQ Status1                              | 37 |

| 9.2.35. REG 49: | IRQ Status2                              | 37 |

| 9.2.36. REG F3: | VREF & Temperature Warning Level Setting | 37 |

| 9.2.37. REG FE: | Serial Interface Address Extension       | 38 |

| 9.2.38. REG FF: | Register Address Extension               | 38 |

| 10. Package     |                                          | 39 |

|                 |                                          |    |

### **1. Overview**

AXP805 is a highly integrated power management IC(PMIC) for 5V inputs and it provides multiple high current power supply. For high-performance multi-core system, AXP805 comes with multi-phase power supply that supports up to 7.5A of current output. It also works with power management chips with battery management capabilities to provide a complete power management solution for power supply system.

AXP805 supports 15 channels power outputs, which includes 5 channels adjustable output buck DC-DC, 10 channels adjustable output LDO. To ensure the security and stability of the power system, AXP805 provides protection circuits such as over-voltage protection(OVP), under-voltage protection(UVP), over-current protection(OCP) and over-temperature protection(OTP), and it provides a high-speed serial interface at the same time, so that the application processor can easily adjust the output voltage of each channel.

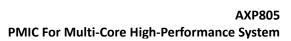

AXP805 is available in 7mm x 7mm 56-pin QFN package.

### 2. Feature

#### • 5-CH DCDC

- DCDC-A: PFM/PWM

- 0.6V~1.1V, 10mV/step, 51steps; 1.12V~1.52V, 20mV/step, 21steps; IMAX = 2.5A

- DCDC-B: PFM/PWM

1.0V~2.55V, 50mV/step, 32steps;

IMAX = 2.5A

- DCDC-C: PFM/PWM

0.6V~1.1V, 10mV/step, 51steps;

1.12V~1.52V, 20mV/step, 21steps; IMAX = 2.5A

- DCDC-D: PFM/PWM

0.6V~1.5V, 20mV/step, 46steps;

1.6V~3.3V, 100mV/step, 18steps;

IMAX = 1.5A

- DCDC-E: PFM/PWM

1.1V~3.4V, 100mV/step, 24steps;

IMAX = 1.5A

- Poly-Phase

- DCDC A&B: Dual-phase, IMAX = 5A

- DCDC A&B&C: Tri-phase, IMAX = 7.5A

- DCDC D&E: Dual-phase, IMAX = 3A

- Other feature: switching frequency: 3MHz,

- 1.5uH/1uH, internal soft-starting, DCDC A/C/D support DVM

- 10-CH LDO

- ALDO1: 0.7V~3.3V, 100mV/step,27steps,

IMAX = 300mA, Input Power is ALDOIN

- ALDO2: 0.7V~3.3V, 100mV/step, 27steps,

IMAX = 300mA, Input Power is ALDOIN

- ALDO3: 0.7V~3.3V, 100mV/step,27steps,

IMAX = 300mA, Input Power is ALDOIN

- BLDO1: 0.7V~1.9V, 100mV/step,13steps,

IMAX = 400mA, Input Power is BLDOIN

- BLDO2: 0.7V~1.9V, 100mV/step, 13steps,

IMAX = 300mA, Input Power is BLDOIN

- BLDO3: 0.7V~1.9V, 100mV/step, 13steps,

IMAX = 200mA, Input Power is BLDOIN

- BLDO4: 0.7V~1.9V, 100mV/step, 13steps,

IMAX = 200mA, Input Power is BLDOIN

- CLDO1: 0.7V~3.3V, 100mV/step,27steps,

IMAX = 400mA, Input Power is CLDOIN

- CLDO2: 0.7V~3.4V, 100mV/step, 28steps,

3.6~4.2V, 200mV/step, 4steps,

IMAX = 300mA, Input Power is CLDOIN

- CLDO3: 0.7~3.3V, 100mV/step, 27steps,

- IMAX = 200mA, Input Power is CLDOIN

- Supports TWSI(Two Wire Serial Interface) protocol, Address is 0x6C/0x6D

- IRQ is an open drain output

- Internal over temperature protection

- Internal voltage monitor, monitors the output voltage of DCDC A/B/C/D/E, internal outputs PWR OK (open drain)signal

- Power on-off key

- On/Off: Typical value of on-resistance is 90 mΩ

- Package: QFN 7x7, 56-pin

- Applications

- STB

- OTT

- -Tablet

- Smart phone

- Computer

### **3. Typical Application**

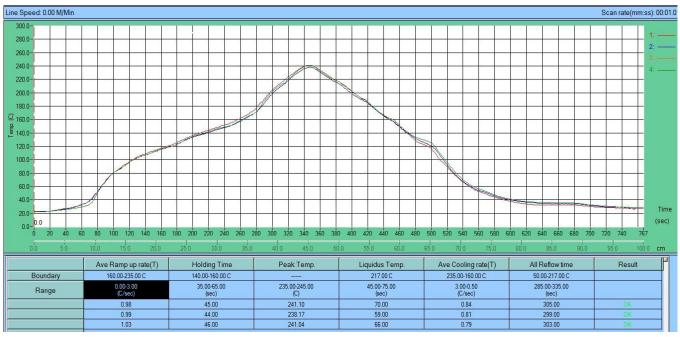

Figure 1. Typical Application

### 4. Block Diagram

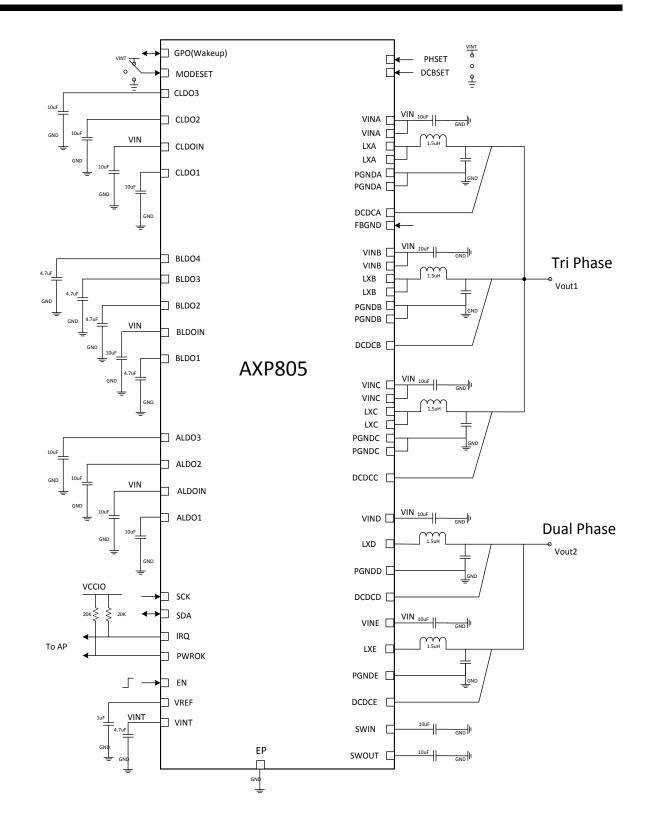

Figure 2. Block Diagram

### 5. Pin Description

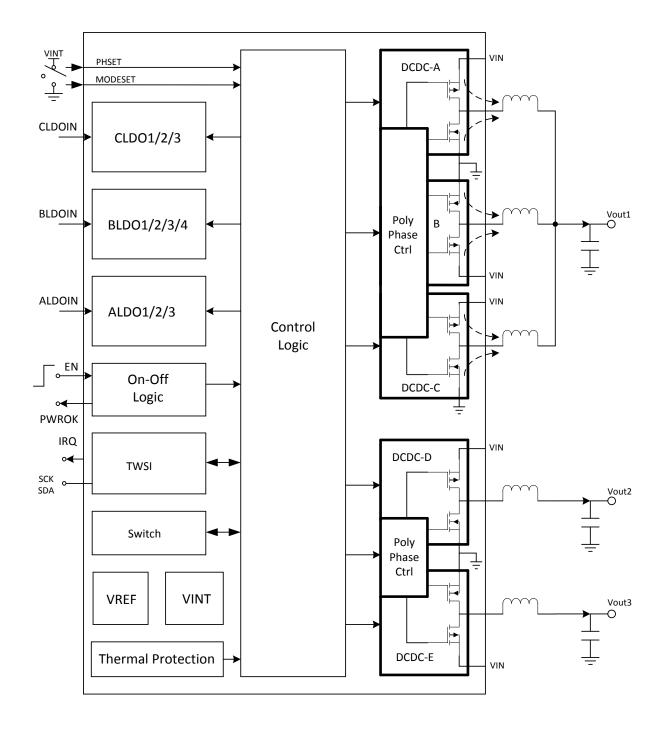

Figure 3. QFN-56

| NO.      | Symbol | Туре       | Description            |    |

|----------|--------|------------|------------------------|----|

| 1        | BLDO2  | 0          | Output pin of BLDO2    |    |

| 2        | BLDO1  | 0          | Output pin of BLDO1    |    |

| 3        | BLDOIN | PI         | BLDOs input source     |    |

| 4        | BLDO3  | 0          | Output pin of BLDO3    |    |

| 5        | BLDO4  | 0          | Output pin of BLDO4    |    |

| 6        | VIND   | PI         | DCDCD input source     |    |

| 7        | LXD    | 10         | Inductor pin for DCDCD |    |

| 8        | PGNDD  | G          | NMOS GND for DCDCD     |    |

| Devision | 1.0    | Comunicala |                        | 10 |

| 10     DCDCE     I     Feedback pin for DCDCE       11     PGNDE     G     NMOS GND for DCDCE       12     LXE     IO     Inductor pin for DCDCE       13     VINE     PI     DCDCE input source       14     GPO     IO     GPO or Wakeup pin by REG35       15     PWROK     O     Power good indication output       16     IRQ     O     IRQ output fin of CLDO3       17     CLDO3     O     Output pin of CLDO1       20     CLDO1     O     Output pin of CLDO1       21     SWIN     PI     Switch input source       22     SWIN     PI     Switch input source       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Enable pin for PMIC in master/slave mode.       27     EN     I     Enable pin for ALDO1       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       36     IXB     IO     Output pin of ALDO2   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |        |    | This for Matt-core fight enormance system                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|----|------------------------------------------------------------------|

| 11     PGNDE     G     NMOS GND for DCDCE       12     LKE     IO     Inductor pin for DCDCE       13     VINE     PI     DCDCE input source       14     GPO     IO     GPO or Wakeup pin by REG35       15     PWROK     O     Power good indication output       16     IRQ     O     IRQ output       17     CLDO3     O     Output pin of CLDO3       18     CLDOIN     PI     CLDO2 O       19     CLDO1     O     Output pin of CLDO2       21     SWIN     PI     Switch input source       22     SWOUT     O     Switch Output pin of CLDO2       21     SWIN     PI     Switch Output pin of CLDO2       22     SWOUT     O     Switch Output pin of CLDO2       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Internal logic power. 1.8V       25     VINT     O     Internal logic power. 1.8V       26     PHSET     I     Enable pin for PMIC in master/slave mode.       27     EN     I     Enable pin for DCDCA       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9  | DCDCD  | 1  | Feedback pin for DCDCD                                           |

| 12     IXE     IO     Inductor pin for DCDCE       13     VINE     PI     DCDCE input source       14     GPO     IO     GPO or Wakeup pin by REG35       15     PWROK     O     Power good indication output       16     IRQ     O     IRQ output       17     CLD03     O     Output pin of CLD03       18     CLDO1N     PI     CLDo input source       19     CLD01     O     Output pin of CLD01       20     CLD02     O     Output pin of CLD02       21     SWIN     PI     Switch input source       22     SWOUT     O     Switch output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/8/C work mode (lonel/Dual-phase/Tri-phase)       27     EN     I     Or PWKOR pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO2N     PI     ALDO3 input source </td <td>10</td> <td>DCDCE</td> <td>1</td> <td>Feedback pin for DCDCE</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 | DCDCE  | 1  | Feedback pin for DCDCE                                           |

| 13     VINE     PI     DCDCE input source       14     GPO     IO     GPO or Wakeup pin by REG35       15     PWROK     O     Power good indication output       16     IRQ     O     IRQ output       17     CLDO3     O     Output pin of CLDO3       18     CLDO1     PI     CLDO3       0     CLDO2     O     Output pin of CLDO1       20     CLDO2     O     Output pin of CLDO2       21     SWIN     PI     Switch input source       22     SWOUT     O     Switch input source       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Internal logic power, 1.8V       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Enable pin for PMIC in master/slave mode.       27     EN     I     Or PWRON pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO2     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       31     ALDO3     O     Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 | PGNDE  | G  | NMOS GND for DCDCE                                               |

| 14     GP0     IO     GPO or Wakeup pin by REG35       15     PWROK     O     Power good indication output       16     IRQ     O     IRQ output       17     CLDO3     O     Output pin of CLDO3       18     CLDO1N     PI     CLDO3 input source       19     CLDO2     O     Output pin of CLDO2       20     CLDO2     O     Output pin of CLDO2       21     SWIN     PI     Switch four put pin       22     SWOUT     O     Switch four put pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Internal logic power, 1.8V       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/8/C work mode.       27     EN     I     Enable pin for PMIC In master/slave mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       31     ALDO2     O     Output pin of nDCDCB       33     UNB     PI     ALDO3 input source       34     VINB     PI     OCCB input source       35     LXB     IO     Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 | LXE    | 10 | Inductor pin for DCDCE                                           |

| 15     PWROK     0     Power good indication output       16     IRQ     0     IRQ output       17     CLD03     0     Output pin of CLD03       18     CLDOIN     PI     CLDOs input source       19     CLD01     0     Output pin of CLD02       20     CLD02     0     Output pin of CLD02       21     SWIN     PI     Switch input source       22     SWOUT     0     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Internal logic power, 1.8V       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Enable pin for PMIC in master/slave mode.<br>(Ionely/Dual-phase/Tri-phase)       27     EN     I     Enable pin for PMIC in master/slave mode.<br>Or PWRON pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO1N     PI     ALDO2 input source       31     ALDO2     O     Output pin of ALDO1       33     VINB     PI     DCDCB input source       34     VINB     PI     Eedback pin for DCDCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 | VINE   | PI | DCDCE input source                                               |

| 16     IRQ     0     IRQ output       17     CLD03     0     Output pin of CLD03       18     CLDOIN     PI     CLD03 input source       19     CLD01     0     Output pin of CLD01       20     CLD02     0     Output pin of CLD02       21     SWIN     PI     Switch input source       22     SWOUT     0     Switch input source       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Enable pin for PMIC in master/slave mode.       27     EN     I     Enable pin for ALD01       29     VREF     O     Internal reference voltage       30     ALD01     O     Output pin of ALD02       31     ALD02     O     Output pin of ALD03       32     ALD03     O     Output pin of ALD03       33     VINB     PI     DCDCB input source       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14 | GPO    | 10 | GPO or Wakeup pin by REG35                                       |

| 17       CLD03       0       Output pin of CLD03         18       CLDOIN       PI       CLD0s input source         19       CLD01       0       Output pin of CLD01         20       CLD02       0       Output pin of CLD02         21       SWIN       PI       Switch input source         22       SWOUT       0       Switch input source         23       SCK       I       Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.         24       SDA       IO       Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.         25       VINT       O       Internal logic power, 1.8V         26       PHSET       I       Set DCDCA/B/C work mode (for PWROM pin in self-work mode.         27       EN       I       Enable pin for PMIC in master/slave mode.         28       ALD01       O       Output pin of ALD01         29       VREF       O       Internal reference voltage         31       ALD02       O       Output pin of ALD02         32       ALD03       O       Output pin of DCDCB         33       YINB       PI       DCDCB input source         34       DC       Output pin of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15 | PWROK  | 0  | Power good indication output                                     |

| 18     CLDOIN     PI     CLDOs input source       19     CLDO1     0     Output pin of CLDO1       20     CLDO2     0     Output pin of CLDO2       21     SWIN     PI     Switch input source       22     SWOUT     0     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/B/C work mode (lonely/Dual-phase/Tri-phase)       27     EN     I     Or PWRON pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       31     ALDO2     O     Output pin of ALDO2       32     ALDO3     O     Output pin of or DCDCB       33     VINB     PI     DCDCB input source       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       36     LXB     IO     Inductor pin for DCDCA       37     PGNDA     G     NMOS GND for DCDCA </td <td>16</td> <td>IRQ</td> <td>0</td> <td>IRQ output</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 | IRQ    | 0  | IRQ output                                                       |

| 19     CLDO1     0     Output pin of CLDO1       20     CLDO2     0     Output pin of CLDO2       21     SWIN     PI     Switch input source       22     SWOUT     0     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm<br>resistor while use TWSI.       24     SDA     IO     Internal logic power, 1.8V       25     VINT     0     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/BC work mode<br>(Ionel//Dual-phase/Tri-phase)       27     EN     I     Enable pin for PMIC in master/slave mode.<br>Or PWRON pin in self-work mode.       28     ALDO1     0     Output pin of ALDO1       29     VREF     0     Internal reference voltage       30     ALDO1     PI     ALDO2       31     ALDO2     0     Output pin of ALDO2       32     ALDO3     0     Output pin of ALDO3       33     The pendence     Inductor pin for DCDCB       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       36     IXB     IO     Inductor pin for DCDCB       37     PGNDB     G     NMOS GND for DCDCA       38 <td< td=""><td>17</td><td>CLDO3</td><td>0</td><td>Output pin of CLDO3</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 | CLDO3  | 0  | Output pin of CLDO3                                              |

| 20     CLDO2     O     Output pin of CLDO2       21     SWIN     PI     Switch input source       22     SWOUT     O     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm<br>resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm<br>resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/8/C work mode<br>(Ionely/Dual-phase/Tri-phase)       27     EN     I     Enable pin for PMIC in master/slave mode.<br>Or PWROND in in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO1N     PI     ALDO2 input source       31     ALDO2     O     Output pin of ALDO3       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       36     VINB     PI     Feedback pin for DCDCB       37     PGNDA     G     NMOS GND for DCDCA       38     DCDCA     I     Feedback pin for DCDCA       41     PGNDA     G     NMOS GND for DCDCA       42     VINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 | CLDOIN | PI | CLDOs input source                                               |

| 21     SWIN     PI     Switch input source       22     SWOUT     O     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm<br>resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm<br>resistor while use TWSI.       25     VINT     O     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/B/C work mode<br>(Ionely/Dual-phase)Tri-phase)       27     EN     I     Enable pin for PMIC in master/slave mode.<br>Or PWRON pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO1     O     Output pin of ALDO2       31     ALDO2     O     Output pin of ALDO3       33     VINB     PI     DCDCB input source       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       39     DCDCA     I     Feedback pin for DCDCA       41     PGNDA     G     NMOS GND for DCDCA       42     PGNDA     G     NMOS GND for DCDCA       43     LXA     IO     Inductor pin for DCDCA       44     LXA <t< td=""><td>19</td><td>CLDO1</td><td>0</td><td>Output pin of CLDO1</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 | CLDO1  | 0  | Output pin of CLDO1                                              |

| 22     SWOUT     0     Switch Output pin       23     SCK     I     Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       24     SDA     IO     Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.       25     VINT     0     Internal logic power, 1.8V       26     PHSET     I     Set DCDCA/B/C work mode (Ionely/Dual-phase)Tri-phase)       27     EN     I     Enable pin for PMIC in master/slave mode.<br>Or PWRON pin in self-work mode.       28     ALDO1     O     Output pin of ALDO1       29     VREF     O     Internal reference voltage       30     ALDO1     PI     ALDO3 input source       31     ALDO2     O     Output pin of ALDO2       33     VINB     PI     DCDCB input source       34     VINB     PI     DCDCB input source       35     LXB     IO     Inductor pin for DCDCB       36     LXB     I     Feedback pin for DCDCA       37     PGNDB     G     NMOS GND for DCDCA       38     DCDCB     I     Feedback pin for DCDCA       41     PGNDA     G     NMOS GND for DCDCA       42     VINA     PI     DCDCA input source       44     LXA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 | CLDO2  | 0  | Output pin of CLDO2                                              |

| 23       SCK       I       Clock pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.         24       SDA       IO       Data pin for serial interface. Connected to IO power by 2.2kohm resistor while use TWSI.         25       VINT       O       Internal logic power, 1.8V         26       PHSET       I       Set DCDCA/B/C work mode (Ionely/Dual-phase)Tri-phase)         27       EN       I       Enable pin for PMIC in master/slave mode.         28       ALDO1       O       Output pin of ALDO1         29       VREF       O       Internal reference voltage         30       ALDO2       O       Output pin of ALDO1         31       ALDO2       O       Output pin of ALDO3         33       VINB       PI       DCDCB input source         34       VINB       PI       DCDCB input source         35       LXB       IO       Inductor pin for DCDCB         36       LXB       IO       Inductor pin for DCDCB         37       PGNDB       G       NMOS GND for DCDCB         38       DCDCB       I       Feedback pin for DCDCB         39       DCDCB       I       Feedback pin for DCDCA         41       PGNDA       G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21 | SWIN   | PI | Switch input source                                              |